# Besi Hybrid Bonding Presentation December 2021

# Safe Harbor Statement

This presentation contains statements about management's future expectations, plans and prospects of our business that constitute forward-looking statements, which are found in various places throughout the press release, including, but not limited to, statements relating to expectations of orders, net sales, product shipments, expenses, timing of purchases of assembly equipment by customers, gross margins, operating results and capital expenditures. The use of words such as "anticipate", "estimate", "expect", "can", "intend", "believes", "may", "plan", "predict", "project", "forecast", "will", "would", and similar expressions are intended to identify forward looking statements, although not all forward looking statements contain these identifying words. The financial guidance set forth under the heading "Outlook" contains such forward looking statements. While these forward looking statements represent our judgments and expectations concerning the development of our business, a number of risks, uncertainties and other important factors could cause actual developments and results to differ materially from those contained in forward looking statements, including any inability to maintain continued demand for our products; failure of anticipated orders to materialize or postponement or cancellation of orders, generally without charges; the volatility in the demand for semiconductors and our products and services; the extent and duration of the COVID-19 pandemic and measures taken to contain the outbreak, and the associated adverse impacts on the global economy, financial markets, and our operations as well as those of our customers and suppliers; failure to develop new and enhanced products and introduce them at competitive price levels; failure to adequately decrease costs and expenses as revenues decline; loss of significant customers, including through industry consolidation or the emergence of industry alliances; lengthening of the sales cycle; acts of terrorism and violence; disruption or failure of our information technology systems; inability to forecast demand and inventory levels for our products; the integrity of product pricing and protection of our intellectual property in foreign jurisdictions; risks, such as changes in trade regulations, currency fluctuations, political instability and war, associated with substantial foreign customers, suppliers and foreign manufacturing operations, particularly to the extent occurring in the Asia Pacific region; potential instability in foreign capital markets; the risk of failure to successfully manage our diverse operations; any inability to attract and retain skilled personnel including as a result of restrictions on immigration, travel or the availability of visas for skilled technology workers as a result of the COVID-19 pandemic; those additional risk factors set forth in Besi's annual report for the year ended December 31, 2020 and other key factors that could adversely affect our businesses and financial performance contained in our filings and reports, including our statutory consolidated statements. We expressly disclaim any obligation to update or alter our forward-looking statements whether as a result of new information, future events or otherwise.

# Agenda

- Overview

- Hybrid Bonding Opportunity

- Q&A

- Richard Blickman, CEO

- Ruurd Boomsma, CTO

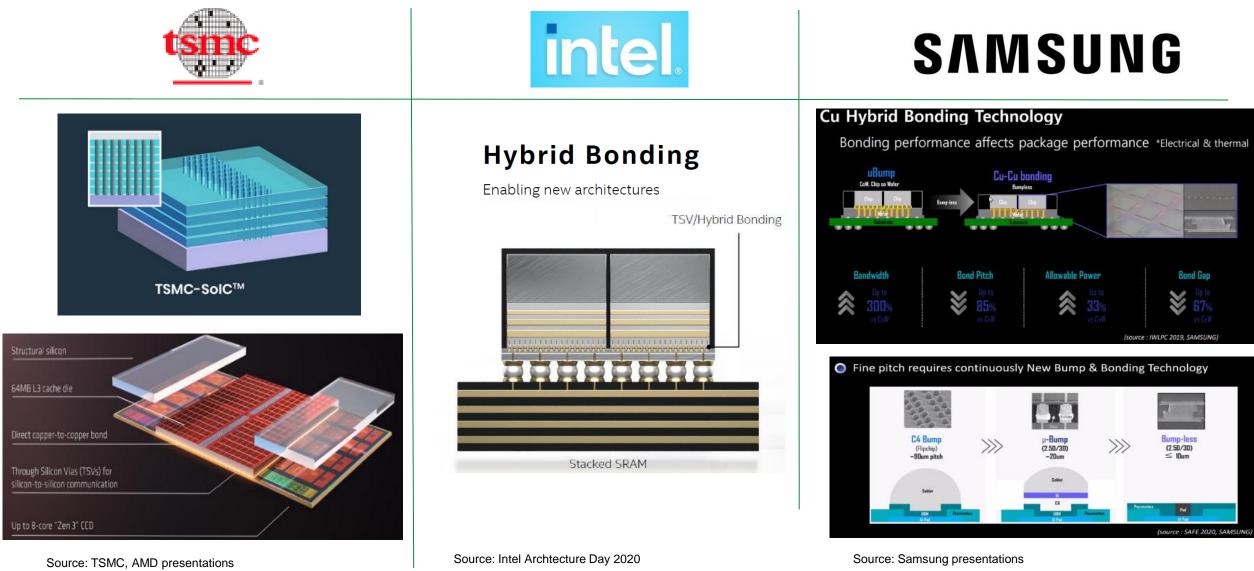

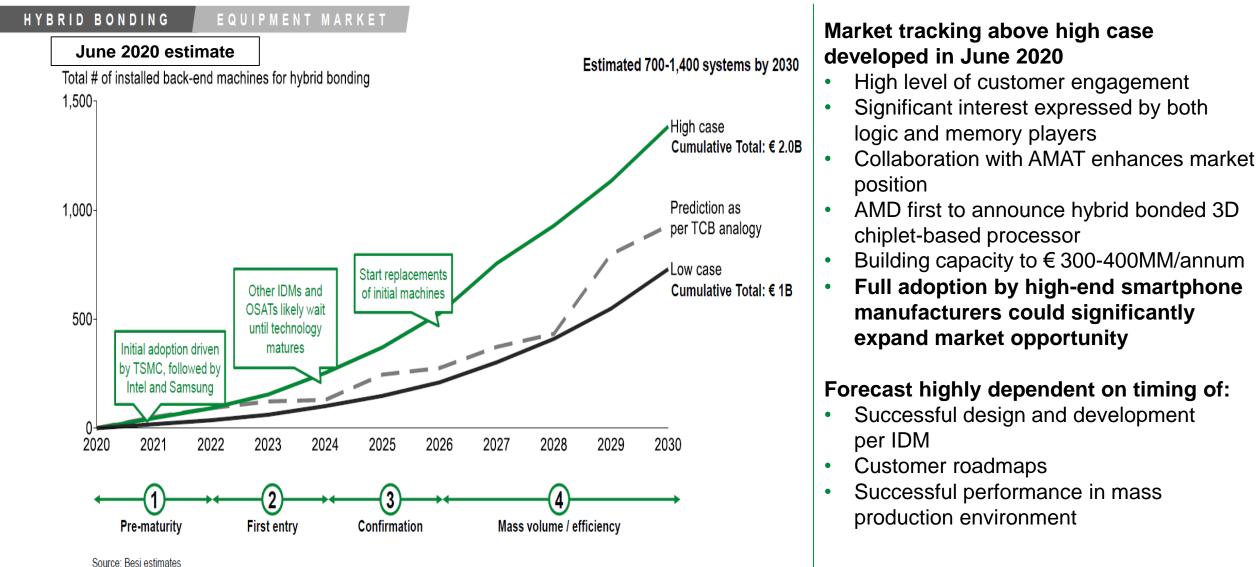

- Semiconductor assembly has moved from individual chip component circuitry to integration on chip level via hybrid bonding. Gating item for semiconductor development

- Hybrid bonding adoption has become most critical element to increasing circuitry speed and further reducing cost

- Has potential to become leading technology for <7nm nodes</li>

- Will coexist with TCB/advanced flip chip and drive growth of high end assembly equipment market

- All leading semiconductor producers evaluating technology

- Market has potential to significantly exceed initial expectations

- Besi has a leading position with competitive advantage

## **Status Today**

- Initial proof-of-concept orders received in Spring 2021

- Additional orders received in both Q2 and Q3-21 for delivery in H1-22

- Cluster tools available in Q1-22 to help support volume production

- Multiple customer engagements

## Capacity/Support Expanded

- Expanded R&D teams in Europe and Singapore

- Completed clean room facility Austria (Q1)

- Added clean room production facility Malaysia (Q4)

- Building capacity to produce 12-15 systems per month

- Engineers and software developers hired for US and Taiwan support

Res

Agenda

- Hybrid Bonding Opportunity

- Q&A

Overview

Richard Blickman, CEO

Ruurd Boomsma, CTO

Besi

# Semiconductor Value Chain

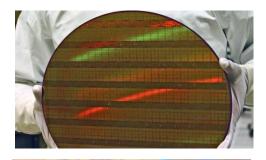

#### FRONT-END

CREATING ELECTRONIC DEVICE ON SILICON WAFER FROM SIMPLE DIODE TO HIGHLY COMPLEX ICs

nanometers

Source: Intel, Anandtech

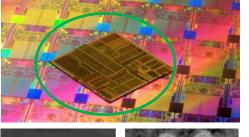

EQUIPMENT TO PLACE DIES ON CARRIER CONNECT TO OUTSIDE WORLD PROTECTING THE DIE COMBINING DIES IN PACKAGE

Source: Embedded, ST, System plus consulting

#### PCB

Besi

MOUNTING COMPONENTS CONNECTING

Source: Techinsight

#### **END PRODUCT**

ALMOST ALL PRODUCTS BASED ON OR CONTAIN ELECTRONIC DEVICES

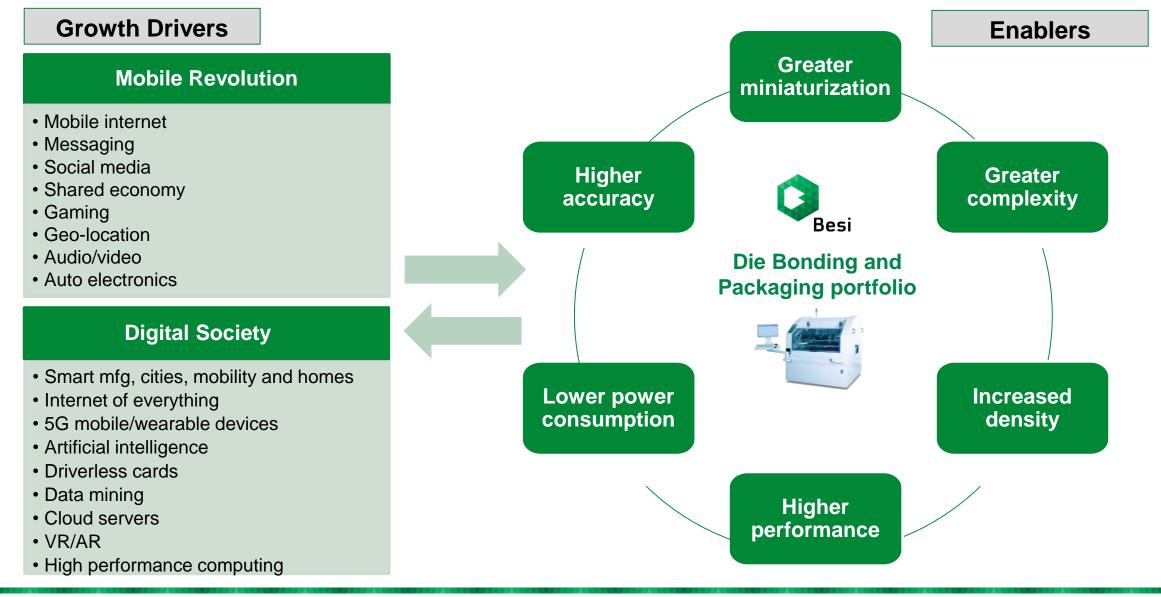

Advanced Packaging Critical to Next Generation Applications

## Growth in Advanced Packaging Will Continue as Gateway to Realizing Improved Performance in Next Gen Applications

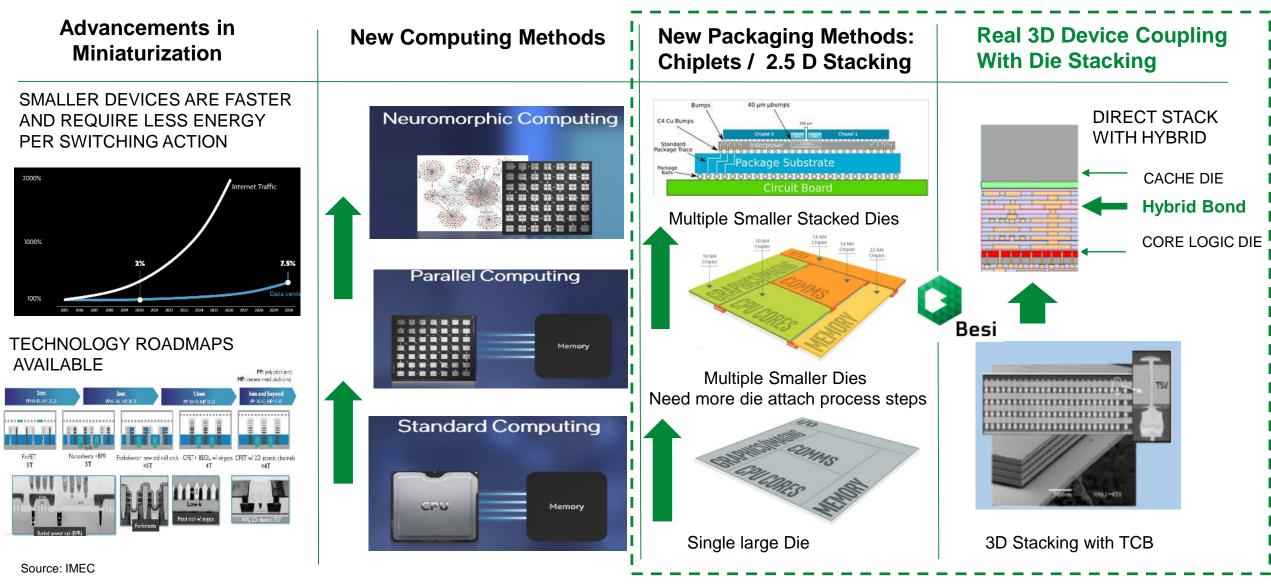

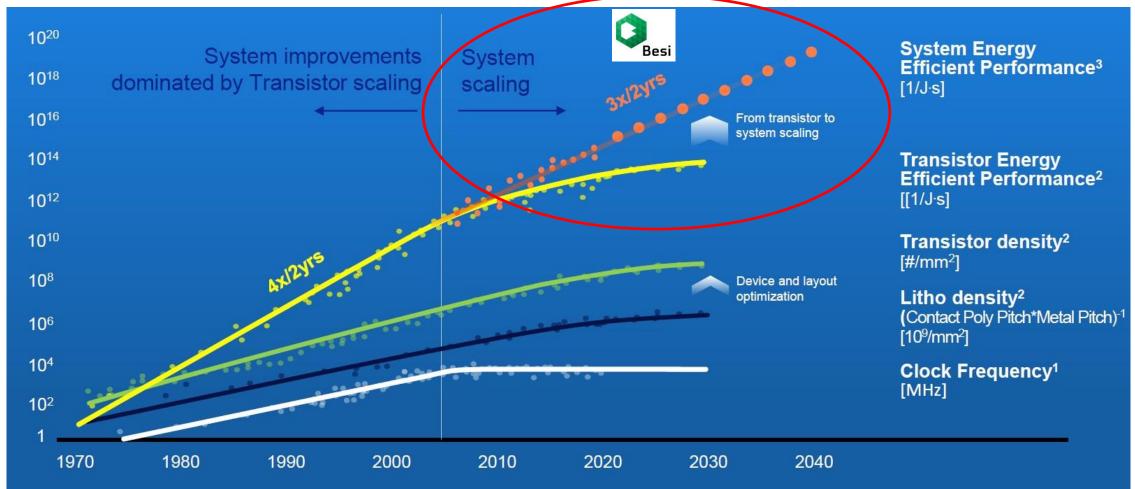

# Moore's law evolution: the next decade

System scaling to satisfy the need for performance and energy consumption

# Hybrid Die Bonding: Next Generation Bonding Technology

|                             |                                    |                                                    |                                  |                                       | Besi                                           |

|-----------------------------|------------------------------------|----------------------------------------------------|----------------------------------|---------------------------------------|------------------------------------------------|

| Wire                        | Bond (1975)                        | Flip Chip (1995)                                   | TCB Bonding (2012)               | HD Fan Out (2015)                     | Hybrid Bonding (2018)                          |

|                             | РСВ                                | PCB                                                | Heat compression force           | Custom Digital                        | Cu Dielectric<br>Cu material<br>Hybrid bonding |

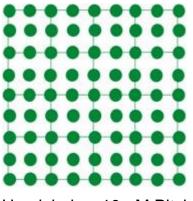

| Density: 5-10/m             | m <sup>2</sup> Contact: wire       | Density: 25-400/mm² Contact:                       | Density: 156-625/mm <sup>2</sup> | Density: 500+ /mm <sup>2</sup>        | Density: 10K-1MM/mm <sup>2</sup>               |

| Spacing <sup>1</sup> :      | 100-50µm                           | 200-100µm                                          | 80-40µm                          | 100-30μm                              | 20-1µm                                         |

| Accuracy <sup>2</sup> :     | 20-10µm                            | 10-5µm                                             | 5-1µm                            | 5-1µm                                 | 0.5-0.1µm                                      |

| Energy/Bit:                 | 10pJ/bit                           | 0.5pJ/bit                                          | 0.1pJ/bit                        | 0.5pJ/bit                             | <.05pJ/bit                                     |

| Substrate:                  | Organic/leadframe                  | Organic/leadframe                                  | Organic /Silicon                 | None                                  | None                                           |

| Throughput:                 | High                               | High                                               | Low                              | Medium                                | Medium                                         |

| Cost:                       | Low                                | Medium                                             | High                             | Medium +                              | High                                           |

|                             | Epoxy die bond                     | Create solder bump/Cu pillar on die                | Create Cu pillars on die         | Create Cu pillars on die              | Create Cu bond pads                            |

| Кеу                         | Wire bond                          | Flip chip placement                                | TCB: place, melt solder & bond   | Place dies on fan out carrier         | Polish to atomic flat surface                  |

| Processes <sup>3</sup> :    | Mold                               | Reflow oven for melting solder                     | No reflow oven                   | Wafer mold                            | Hybrid bond (room temp.)                       |

|                             |                                    | Underfill/mold                                     | Underfill/mold                   | Create RDL layers                     | Mold                                           |

| <sup>1</sup> Contact Spacin | ng. <sup>2</sup> Die Placement Acc | curacy. <sup>3</sup> Shading denotes Besi process. |                                  | Densities typical for 8x8 mm die size | 2                                              |

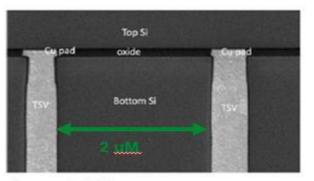

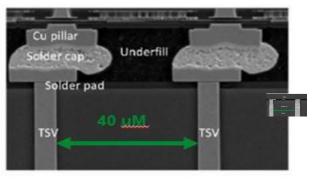

# **Understanding Hybrid Bonding**

2

3

#### Si BEOL Metal Dielectric Metal

#### (Plasma-activated surfaces)

| Metal | Dielectric | Metal |

|-------|------------|-------|

|       | BEOL       |       |

|       | Si         |       |

|       | Si         |       |

|-------|------------|-------|

|       | BEOL       |       |

| Metal | Dielectric | Metal |

| Metal | Dielectric | Metal |

|       | BEOL       |       |

|       | Si         |       |

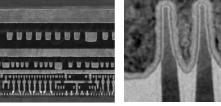

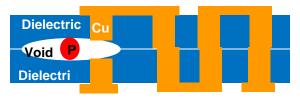

- Preparation

- CMP Polishing

- Very flat < 5nm and clean

- Surface Activation

- Very Clean

- Bonding

- Accurate Placement

- Cold Bond

- Based on initial dielectric bond

#### Si BEOL Metal Dielectric Metal Metal Dielectric Metal BEOL Si

- Cu-Cu Bonding via Anneal

- Copper expands and contact is made

- Depends on dishing

- Depends on Cu properties

#### **Die to Wafer and Die to Die Bonding of Chiplets**

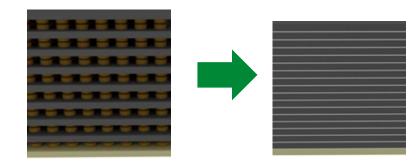

#### DIRECT CU-CU BOND

#### Compare to TCB

Source: XPERI ECTC 2019

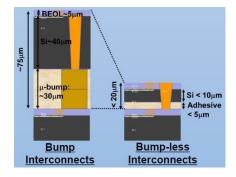

#### **BUMPLESS INTERCONNECT**

Used below 10 µM Pitch and contact ! < 200nM Accurate

# Merges Front-End/Back-End Processes

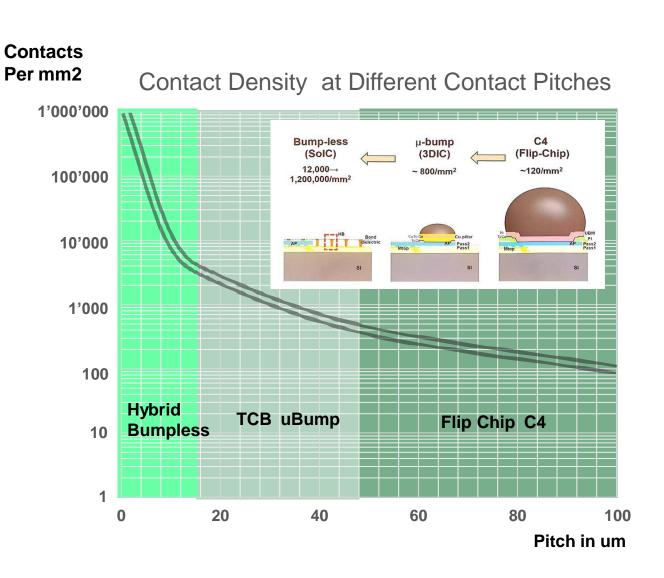

## Reducing cost/contact C4 (Flip-Chip) ~120/mm<sup>2</sup> (Bump-less (SoIC) 12,000-1,200,000/mm<sup>2</sup>

Hybrid die to wafer bonding much like front-end fab

# Align Contacts<br/>Very Precisely<br/>In X and YTypical 10% Max<br/>Deviation of contact size<br/>1 um contact =><br/>100 nm Accuracy

As well as angular control

um Contact on 30 mm die

10% Mismatch at corner

3 mm on 1 km

Approx. 10% mismatch allowed

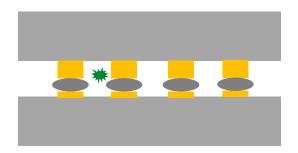

Requiring Higher Levels of Cleanliness Comparable to Front-End <u>Which Drives Upwards ASP</u>

Besi

In TCB process, a small particle may have little effect

In hybrid process, a small particle may cause an open contact

Source: TSMC

December 3, 2021

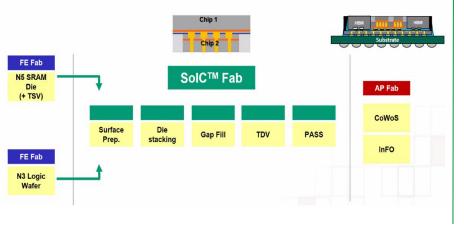

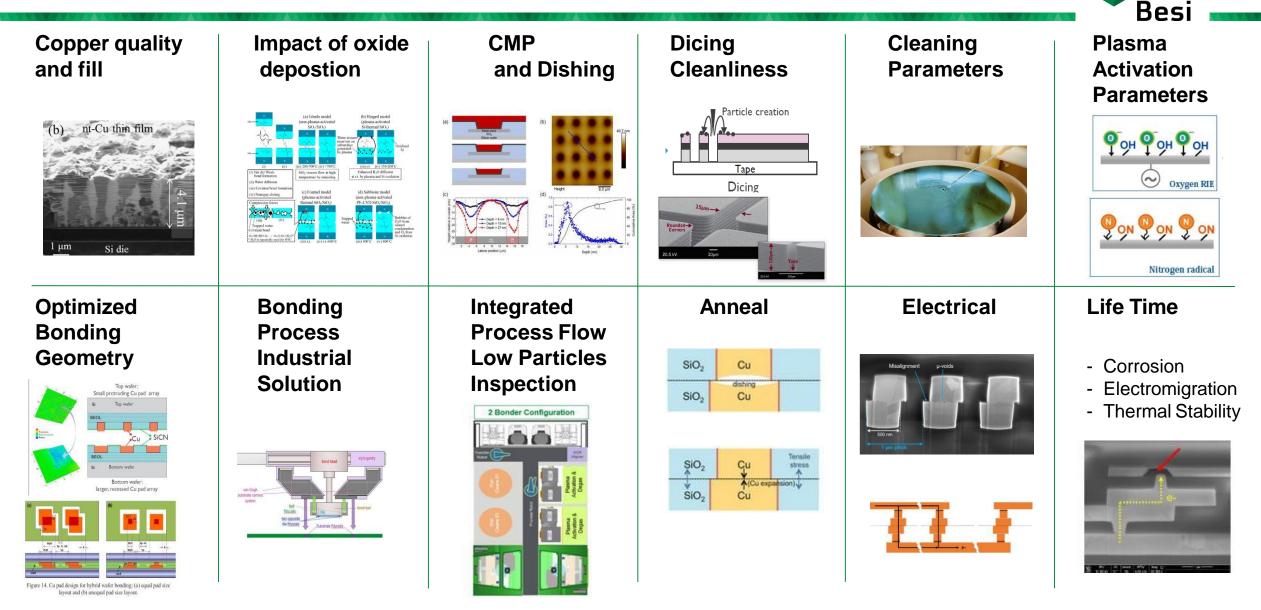

# Many Front-End and Assembly Process Steps Involved in Clean Room Environment

Hybrid Bonding is a Game Changer for Increasing Contact Density

Besi

# 50 um Pitch Lakefield 400 bumps/mm<sup>2</sup> Top View Area scales with bump pitch 10 um Pitch Hybrid Bonding Top View 10000 bumps/mm2

MORE DATA =>MORE CONTACTS

Source: Intel

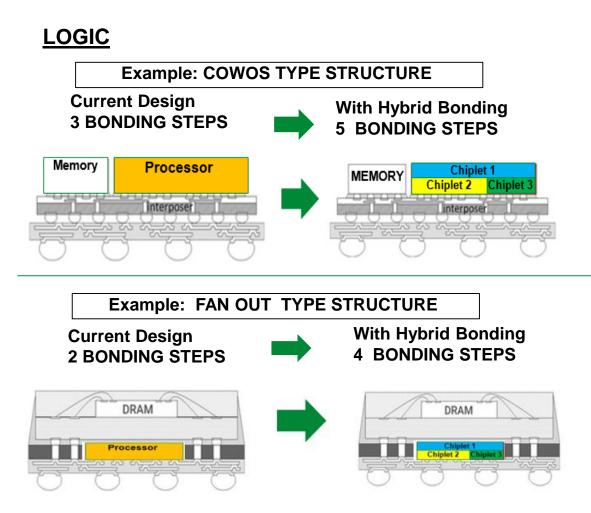

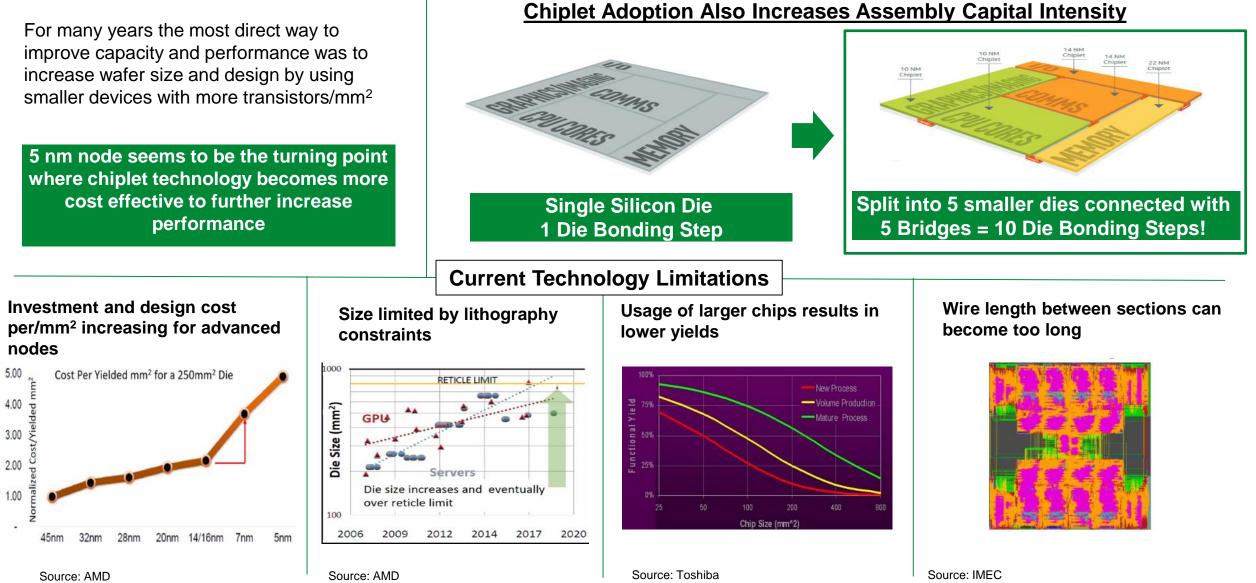

Requires More Process Steps Resulting in Higher Assembly Capital Intensity

Source: TSMC

#### <u>MEMORY</u>

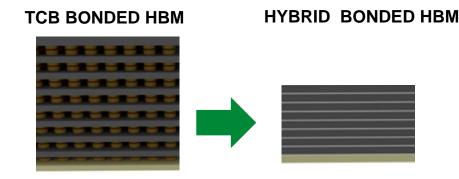

CASE 1 => HYBRID MAY REPLACE 1 TO 1 TCB

#### CASE 2 => HYBRID WILL ALLOW FOR MORE DIES IN SAME STACK HEIGHT LEADING TO MORE BONDING STEPS

Source: Xperi

Besi

# Now on Agenda of All Big Players

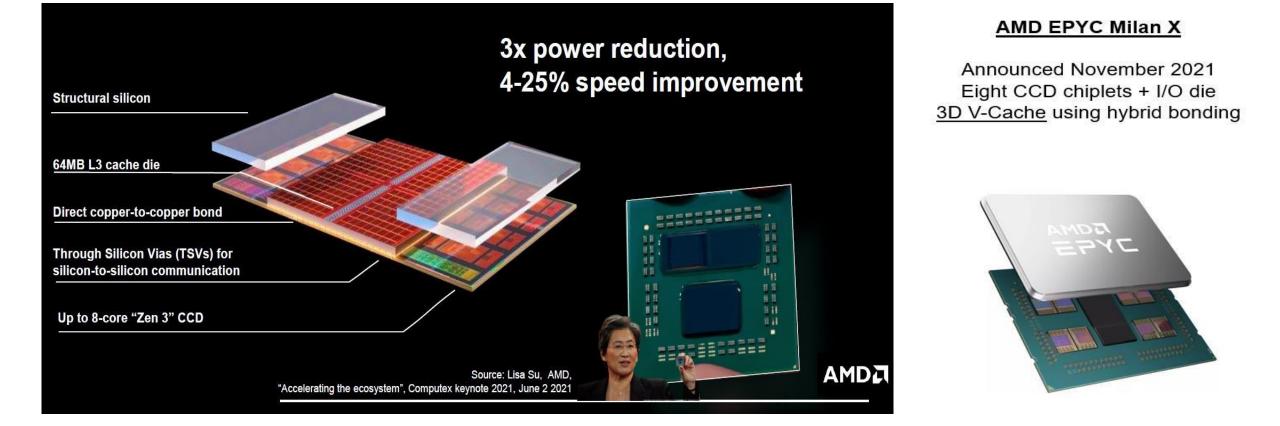

# AMD 3D chiplet gives an 3.1-3.8 EEP improvement By integrating memory with the processor in one package

## Chiplet Adoption Enables Cost Effective Means of Increasing Performance

Hybrid Bonding Adoption Leads to Higher Capital Intensity per UPH

**8800 FC Quantum** 3 micron accuracy

ASP: \$500k

~9,000uph

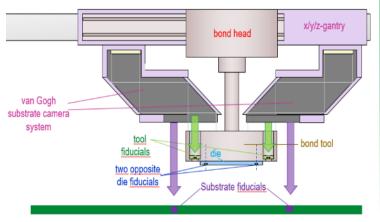

# **8800 Ultra Accurate Chip to Wafer Hybrid Bonder** <200 nanometer accuracy

Pricing: \$1.5MM-2.5MM Configuration dependent

~1,500uph

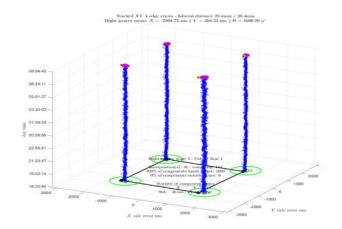

# Status Update: Besi/AMAT Development Cooperation

#### SYSTEM IMPROVEMENTS

REACHING 122nm ACCURACY OUTPUT UP TO 2,000 UPH

High accuracy placement within 200nm radius

JOINT DEVELOPMENT COOPERATION AMAT AND BESI

#### **ANNOUNCED OCTOBER 2020**

- Front and Back-End Process Expertise

- Dedicated Packaging Development Center

- Platform Design and Integration

- Assembly Equipment Process Expertise

- Market Leader in Hybrid Bonding Systems

#### JOINT HYBRID CENTRE IN SINGAPORE JOINT DEVELOPMENT OF CLUSTER SOLUTION

SUBSTANTIAL INVESTMENT IN CLEAN ROOM INFRASTRUCTURE, MEASUREMENT EQUIPMENT, AND PEOPLE

#### Estimated Rollout of Hybrid Bonding Applications Besi 2022 2023 2024 2025 2026 2027 2028 2029 2030 **Computing:** Servers/Datacenter/HPC/AI Consumer: PC/Laptop/Gaming/Entertainment Memory: HBM Mobile: High-end smartphone, watch, Airpods Automotive: Autonomous driving Industrial/Medical

Overview

Hybrid Bonding Opportunity

Q&A

Richard Blickman, CEO

Ruurd Boomsma, CTO